串行数据总线由于占用较少的管脚被广泛应用在MCU和外设的连接中,在过去的几十年里,有三种最常用的多线串行数据传输格式SPI、I2C和UART。这3种串行总线的主要区别:

SPI – Serial Peripheral Interface(串行外设接口),突出了外设,也就有了主(Master – 控制器)和从(Slave – 外设)之分,在总线中也就只有一个“主人”,其它都是处于服从的位置,也就是Slave,它是一种有时钟信号的同步串行总线,从器件的寻址是靠专用的片选信号线SS来实现的;

UART – universal asynchronous receiver/transmitter(通用异步收/发),顾名思义,它是异步串行总线,传输的信号中没有专用的时钟信号线。

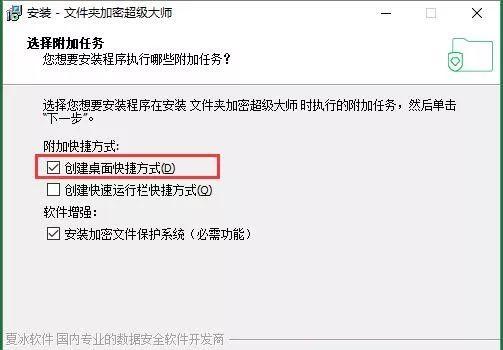

由于很多MCU、外设芯片为了节省管脚,都采用了管脚功能复用的方式,同一个管脚既可以用于SPI,也可以用于I2C,根据具体的器件连接方式进行选用。当器件的管脚配置为I2C的时候,要记住在I2C的两根信号线(SCL、SDA)上一定要有上拉电阻,SPI则不需要。

今天我们就先来说说SPI:

SPI(Serial Peripheral Interface – 串行外设接口)是一种用于短距离通信(主要是嵌入式系统中)的同步串行通信接口规范,这种接口由Motorola发明,已经成了一种事实标准。广泛用于各种MCU处理器中,同传感器,串行ADC、DAC、存储器、SD卡以及LCD等进行数据连接。

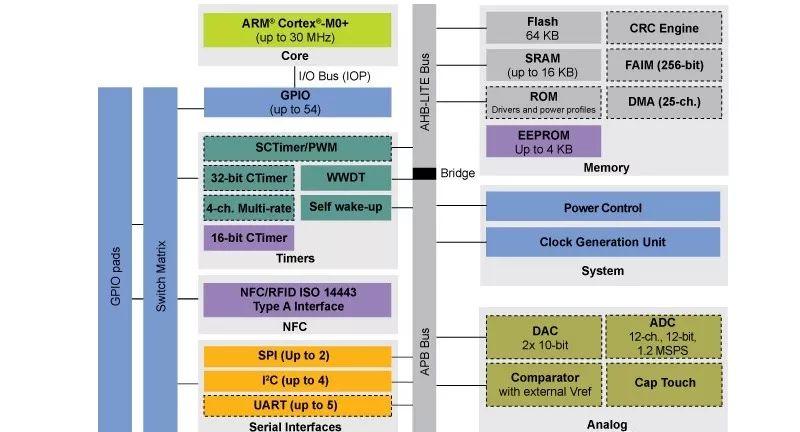

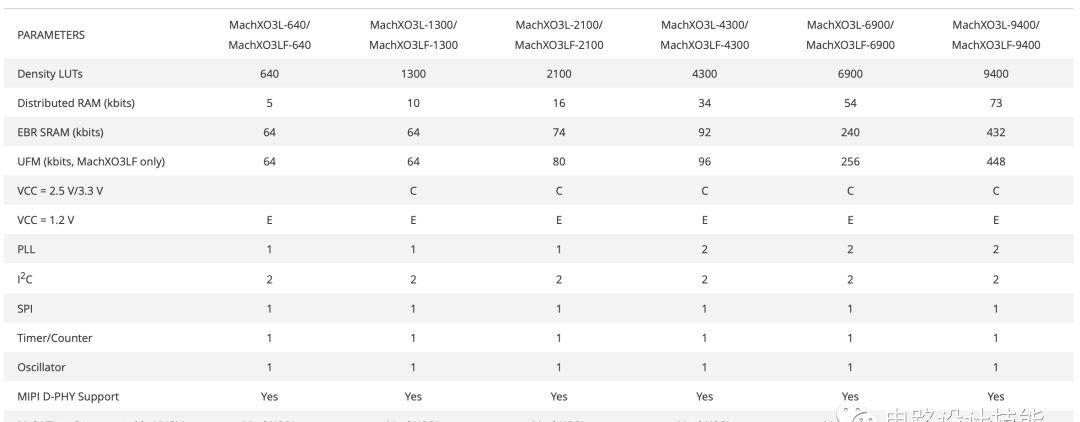

几乎所有的微处理器/微控制器都有SPI/I2C和UART接口,而且不止一个

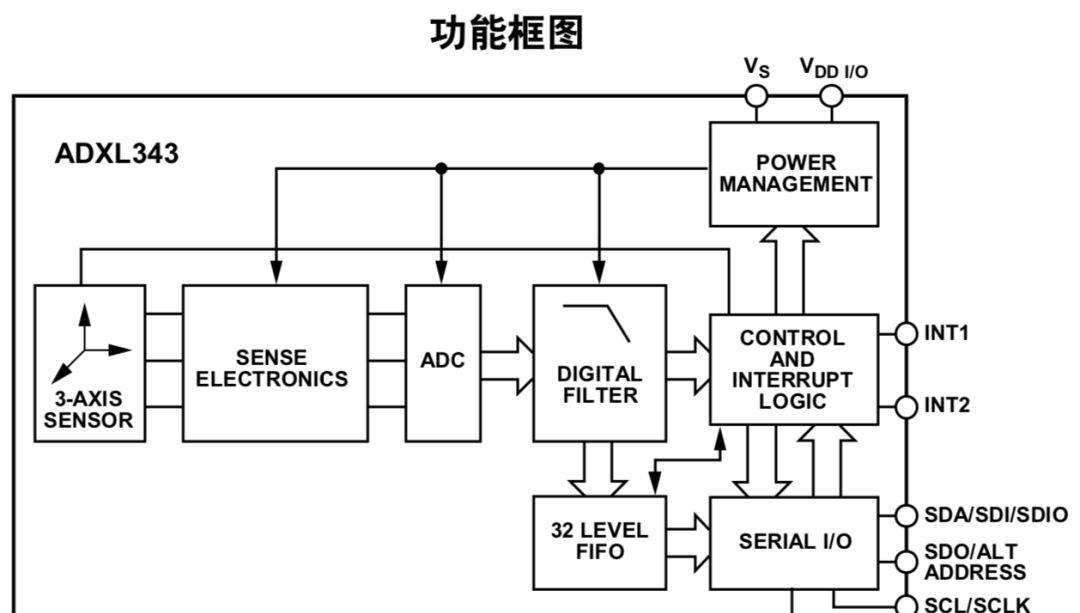

SPI和I2C也被广泛用于传感器的数字接口连接

即便FPGA也将SPI和I2C做成了硬化的IP在芯片内

主要的信号线:

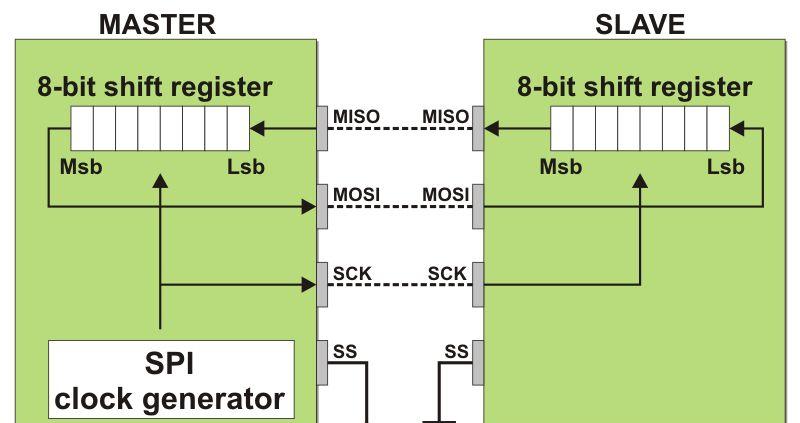

SPI总线由4根主要的信号线组成以实现数据在主设备(Master)和从设备(Slave)之间的全双工(收、发同时执行)同步(由时钟同步)通信:

SCLK:串行时钟(由主设备输出),每个时钟周期将会移出一个新的数据位;

MOSI:主设备输出??从设备输入,数据由主设备进入从设备,器件A上的MOSI线连接到器件B上的MOSI线。

MISO:主设备输入?? 从设备输出,数据由从设备送到主设备(或其它从设备,采用菊花链配置),器件A上的MISO线连接到器件B上的MISO线。

SS(或SSN): 从设备选中(低电平有效),用于主设备控制从设备用,当该从选择信号线有效的时候表示主设备正在向相应的从设备发送数据或从相应的从设备请求数据。

SPI端口管脚的名字也有其它的叫法,不同的芯片公司叫法不同,比如:

串行输出: SCLK : SCK, CLK.

主输出 –> 从输入: MOSI:SIMO、SDI(for slave devices)、DI、DIN、SI、MTST.

主输入 ←从输出: MISO:SOMI、SDO (for slave devices )、DO、DOUT、SO、MRSR.

从选择: SS: SSN、nCS、CS、CSB、CSN、EN、nSS、STE、SYNC.

主从器件之间的连接及数据传输方式

基本的主从配置

SPI允许将数据位从主设备移出到从设备,同时,可以将从设备的位移出到主设备中。

动画1显示数据从器件A移出到器件B,从器件B移出到器件 A.

动画2显示了通过一个虚拟的4通道示波器捕捉的两个器件之间SPI的转换

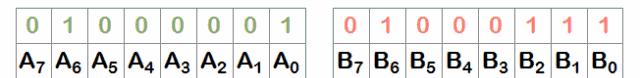

由于SPI未标准化,不同厂商的器件具体的定义不同,有的首先传输最高有效位(MSb),有的则是最低有效位(LSb),这需要我们认真阅读用到的相应器件的数据手册,以确定正确的数据处理方式。

4种传输模式:

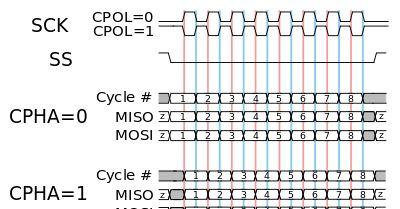

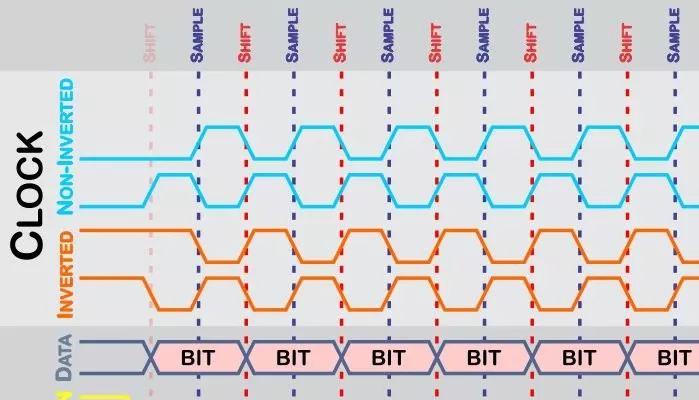

每次数据传输都是先将SSN(有的器件命名为SS,从选择线)被驱动为逻辑低电平时开始。由时钟的极性(CPOL)和相位(CPHA)构成了4种不同的数据传输模式(0,1,2,3),分别对应四种可能的时钟配置。

CPOL:时钟的极性,它控制着时钟信号的初始逻辑状态。

CPHA:时钟相位,它控制了数据转换和时钟转换之间的关系。

时钟的极性和相位构成了4种不同的可能,也就有4种模式

在时钟周期的上升沿采样的位在时钟周期的下降沿移出,反之亦然。

具有非反相时钟极性(即,当从器件选择转换为逻辑低时,时钟处于逻辑低电平):

模式0:配置时钟相位使得数据在时钟脉冲的上升沿采样,并在时钟脉冲的下降沿移出。 这对应于上图中的第一个蓝色时钟轨迹。 请注意,数据必须在时钟的第一个上升沿之前可用。

模式1:配置时钟相位使得数据在时钟脉冲的下降沿采样,并在时钟脉冲的上升沿移出。 这对应于上图中的第二个蓝色时钟轨迹。

使用反相时钟极性(即,当从器件选择转换为逻辑低时,时钟处于逻辑高电平):

模式2:配置时钟相位,使得数据在时钟脉冲的下降沿采样,并在时钟脉冲的上升沿移出。 这对应于上图中的第一个橙色时钟轨迹。 请注意,数据必须在时钟的第一个下降沿之前可用。

模式3:配置时钟相位,使得数据在时钟脉冲的上升沿采样,并在时钟脉冲的下降沿移出。 这对应于上图中的第二个橙色时钟轨迹。

由于主设备一般为可以编程各种模式的控制器/处理器或者可以灵活编程的FPGA,因此在使用SPI连接的时候要认真阅读自己选用的从设备的工作模式,以便在时许上满足传输的要求。

主、从器件连接方式

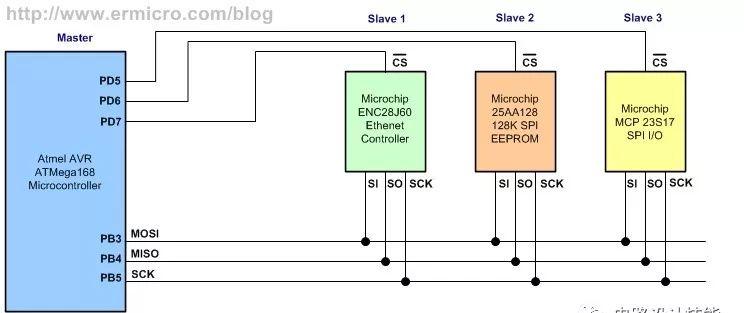

通过多个从片选信号(SSN)配置

在标准的SPI配置中,主设备可以通过使能相应的从设备,即通过将相应设备的从选择线(SSN或SS)设置为逻辑低电平,通过共享的公共数据线将数据写入各个从设备或由各个从设备中读取数据。 应注意不要同时使能多个从设备,因为返回到主设备的数据将在MISO线路之间的驱动器上产生竞争导致无法进行数据的判读。 在某些应用中不需要将数据返回给主设备,在这种情况下,如果主设备想要将相同的数据发送到多个从设备,则可以同时寻址多个从设备。

在多从设备选择配置中,每个从设备都需要来自主设备的唯一从设备选择线(SS、SSN或CSn)。如果主设备没有足够的I/O引脚用于所需数量的从设备,则使用解码/解复用器(例如74HC(T)238(3到8线)来实现I/O扩展)。

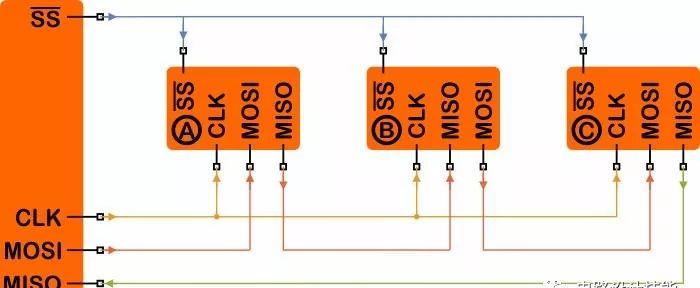

菊花链配置

在这种配置中,数据从一个设备移动到下一个设备, 最终的从设备可以将数据返回给主设备(给FPGA编程的JTAG在给多个器件编程的时候也常用这种方式)。

在菊花链配置中,所有从设备共享一条公共的从选择线(SS)。 数据从主设备传输到第一个从设备,然后从第一个从设备传输到第二个从设备,依此下去,数据沿着线路级联,直到系列中的最后一个从设备,最后的一个从设备使用其MISO线路将数据传送到主设备。

这种配置非常适合于主设备的信号引脚有限的场景。

SPI的优缺点:

优点:

支持全双工通信

推挽驱动(跟漏极开路正相反)提供了比较好的信号完整性和较高的速度

比I??C或SMBus吞吐率更高

协议非常灵活支持“位”传输

不仅限于8-bit一个字节的传输

可任意选择的信息大小、内容、以及用途

异常简单的硬件接口:

一般来讲比I??C或SMBus需要的功耗更低,因为需要更少的电路(包括上拉电阻)

没有仲裁机制或相关的失效模式

“从设备”采用的是“主设备”的时钟,不需要精确的晶振

不需要收/发器

在一个器件上只用了4个管脚, 板上走线和布局连接都比并行接口简单很多

每个设备最多只有一个单独的从设备选择信号(SS、SSN、CSn);其它的都是共享的

信号都是单方向的,非常容易进行电流隔离

对于时钟的速度没有上限,有进一步提高速度的潜力,很多MCU的SPI传输速率可以高达50Msps,可用于数据采集以及图像的传输。

缺点:

相比于I??C总线需要更多的管脚, 即便是只用到3根线的情况下

没有寻址机制,在共享的总线连接时需要通过片选信号支持多个设备的访问

在从设备侧没有硬件流控机制(主设备一侧可以通过延迟到下一个时钟沿以降低传输的速率)

从设备无法进行硬件“应答”(主设备传送的信息无法确定传递到哪里,是否传递成功)

一般只支持一个主设备(取决于设备的硬件构成)

没有查错机制

没有一个正式的标准规范,无法验证一致性

相对于RS-232, RS-485, 或CAN-总线,只能近距离传输

存在很多的变种,很难能够找到开发工具(例如主适配卡)支持这所有的变种

SPI不支持热交换(动态地增加一个节点).

如果想使用“中断”,只有通过SPI信号以外的其它信号线,或者采用类似USB1.1或2.0中的周期性查询的欺骗方式

应用举例:

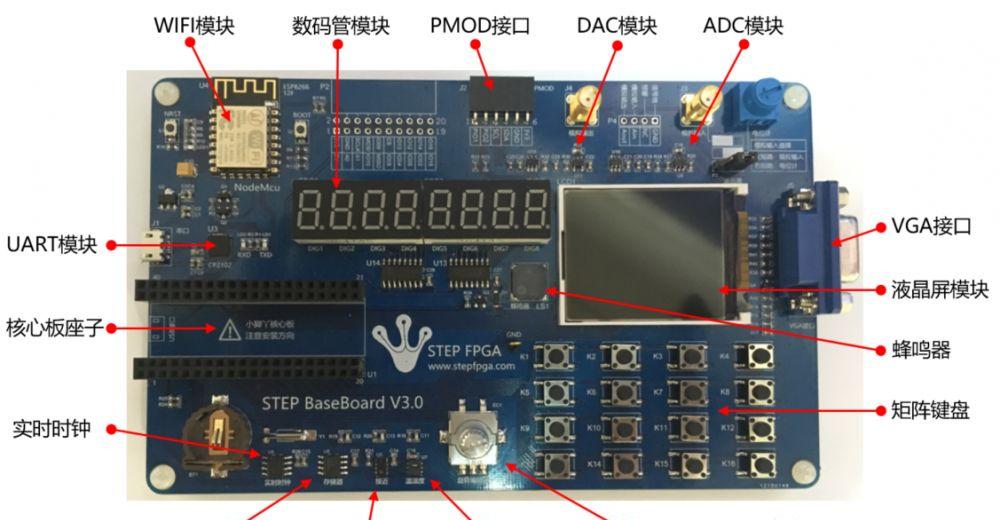

小脚丫FPGA学习主板上的DAC、ADC、以及用于图形显示的液晶屏都是通过SPI接口连接的。

小脚丫FPGA主板的实物照片,外设基本都是通过SPI、I2C以及UART进行连接的

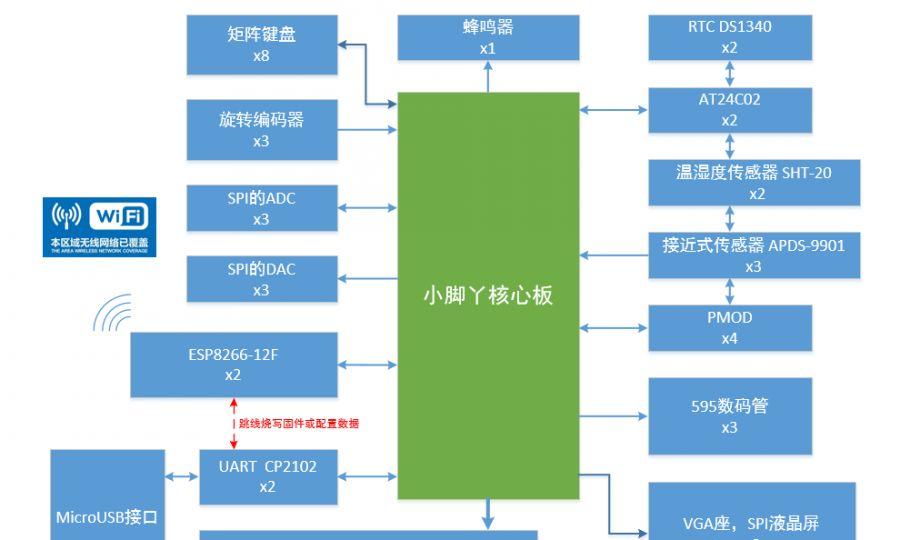

小脚丫FPGA主板的功能框图

鉴于此,我们硬件工程师很有必要深入了解SPI、I2C以及UART的技术细节,尤其是传输信号线的连接以及传输的时序要求,争取能够自己通过FPGA来编程实现各种传输总线。